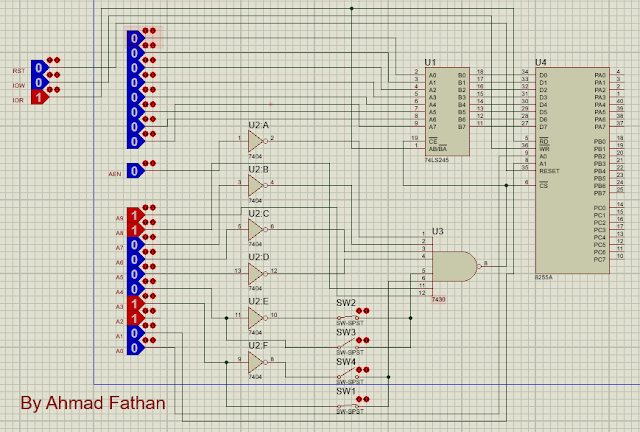

Rangkaian Interface dengan Decoder NAND

- Rancanglah rangkaian interface untuk alamat 30CH

- Rancanglah rangkaian interface untuk alamat 30CH atau 304H

2. Penjelasan [kembali]

Rangkaian di atas adalah rangkaian interface dengan decoder NAND IC 7430. Rangkaian di atas dikendalikan menggunakan PC Bus. Namun untuk mensimulasikan rangkaian tersebut PC Bus diganti dengan Logic Source (Latched). Pada gambar di atas alamat yang dipakai adalah 30CH.

Secara berurutan A0 sampai A11 berlogika 00110001100. A0 dan A1 pada PC Bus terhubung dengan A0 dan A1 pada IC 8255. A0 dan A1 berguna untuk menentukan PORT yang digunakan pada IC 8255. Karena A0 = '0' dan A1 = '0' maka PORT ke-0 atau PORT A yang akan aktif. Selanjutnya A2 sampai A11 kecuali A2, A10, dan A11 berguna untuk mengontrol aktif atau tidaknya IC 8255 dan IC 74LS245. Alamat 30CH mengakibatkan output dari IC NAND 7430 berlogika '0' sehingga IC 8255 dan IC 74LS245 aktif. Selanjutnya pin yang harus dikontrol adalah IOW dan IOR. Kedua pin tersebut 'active Low'. Namun hanya ada 1 pin yang boleh aktif. Ketika IOW berlogika '0' dan IOR berlogika '1' maka alur data adalah dari PC Bus ke buffer IC 74LS245 lalu ke IC 8255. Data akan mengalir sebaliknya jika IOW berlogika '1' dan IOR berlogika '0'.

Rangkaian di atas adalah rangkaian interface dengan decoder NAND IC 7430. Rangkaian di atas dikendalikan menggunakan PC Bus. Namun untuk mensimulasikan rangkaian tersebut PC Bus diganti dengan Logic Source (Latched). Pada gambar di atas alamat yang dipakai adalah 30CH.

Secara berurutan A0 sampai A11 berlogika 00110001100. A0 dan A1 pada PC Bus terhubung dengan A0 dan A1 pada IC 8255. A0 dan A1 berguna untuk menentukan PORT yang digunakan pada IC 8255. Karena A0 = '0' dan A1 = '0' maka PORT ke-0 atau PORT A yang akan aktif. Selanjutnya A2 sampai A11 kecuali A2, A10, dan A11 berguna untuk mengontrol aktif atau tidaknya IC 8255 dan IC 74LS245. Alamat 30CH mengakibatkan output dari IC NAND 7430 berlogika '0' sehingga IC 8255 dan IC 74LS245 aktif. Selanjutnya pin yang harus dikontrol adalah IOW dan IOR. Kedua pin tersebut 'active Low'. Namun hanya ada 1 pin yang boleh aktif. Ketika IOW berlogika '0' dan IOR berlogika '1' maka alur data adalah dari PC Bus ke buffer IC 74LS245 lalu ke IC 8255. Data akan mengalir sebaliknya jika IOW berlogika '1' dan IOR berlogika '0'.

0 komentar:

Posting Komentar